# Power Optimization using Look Ahead Clock Gating

### Ng Kok Why

Faculty of Computing and Informatics, FCI-BR3006, Multimedia University, Persian Multimedia 63100, Cyberjaya, Selangor kwng@mmu.edu.my

Received: 12<sup>th</sup> May 2021, Accepted: 17<sup>th</sup> June 2021, Published: 30<sup>th</sup> June 2021

# **Abstract**

Low power checking is the key element in the process of developing the VLSI. Modern ICs consist of more transistors in a single chip making testing difficult because it uses more power than the functionality of the circuit. A significant part of the dynamic power absorbs the unit clock signal in the electronics network, 70 per cent of which is expended on clock buffers.

Keywords: VLSI, Clock, ICs, Dynamic power

#### Introduction

Strength-designs have seen a major increase in demand in recent years. The rapid development of rechargeable battery technologies, such as portable and cellular modems, personal digital assistants, phones, and other wireless communications devices, was mostly to blame for this great appetite. Because of greater spectral efficiency in a chip and lower starting temperatures, electricity consumption in a kill increases every generation. The input voltage is adjusted to keep energy usage within acceptable limits.

It was also essential to obtain low power. Micro-meter voltage spikes, in conjunction with supply volt scaling models, account for a considerable portion of overall power consumption in high-performance electronic circuits. Because high-performance devices are constrained by an energy schedule, the ability to leak reduces the available power and has an impact on efficiency. This also raises energy consumption throughout the backup service, increasing battery life. As a result, approaches for reducing energy loss while maintaining a healthy efficiency are necessary. Furthermore, when more leaking products come into play in software development, each leak reduction solution must be carefully addressed in scaling situations where post-threshold heat transfer is not the only leaking way.

# Methodology

**Power Dissipation in VLSI Circuits:** Complete output voltage in a circuit is constituted conventionally of two parts, namely the convective cooling of vertical and horizontal energy. There will be two elements for adaptive parasitic capacitance one is swapping power due to loading and charge voltage discharged. The other is the power of the malfunction due to the source waveforms 'finite rise and fall time.

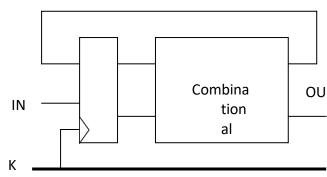

**Clock gating:** Clock gating is an important way to reduce the dissipation of dynamic power in digital circuits. In a typical Synchronous circuit such as a general purpose microprocessor, only a portion of the circuit is involved at any given time. Hence, the excessive power usage can be avoided by shutting down the idle portion of the circuit. One of the ways to achieve this is by masking the clock that goes to the idle portion of the circuit. This avoids improper shifting of data to inactive circuit point, therefore increasing the variable energy. The input to the boolean algebra logic falls via the databases, consisting of consecutive components such as D flip-flops (Fig 1).

Fig 1: Single clock, flip-flop-based FSM

A walled-clock specification can be achieved by modifying the clocking configuration shown in Fig.1. When the combinational block is not used, the Regional Timer (LCLK) is randomly disabled with a command trigger (fa). When fa is high, this blocks the local clock. If the global clock (GCLK) is small, the latch shown in Fig.1.2 is required to prevent the dissemination to the AND gate of any fa errors.

The fa signal also becomes accurate until the climbing edge of the international timer. When the international timer is poor, the trigger is translucent but fa does not even impact the AND windows. If fa is strong during most of the global minute hand small-to-high change, the worldwide clock will be closed by the gate AND and the local clock will stay at low. The microcontroller clock system feeds serial elements like flip-flops and latches, and dynamics Logic doors used in heavy-performance operation units and array message encoders (e.g. D-cache word-line decoder). Cg is the gate powerful capacitance which tends to be a capacitive load to the clock, and CL is the complex cell's multi touch charge. With the lock, the flexible logical Cg also loads and fires per loop, which consumes power.

**Basic Operation of Look Ahead Clock Gating:** Clock gating is quite helpful in limiting the power consumed by the computer devices. There are three documented gating methods. The most famous is ligand binding-based, gleaning clock that allows the fundamental system logic to be driven by the signal. Sadly it makes most clock impulses obsolete controlling the flip-flops (FFs).

A third mechanism identified as self-gated FFs (AGFF) is easy, but generates limited electricity saving. This paper presents Look-AheadC Gating lock (LACG), an unique method that combines all three. LACG calculates the clock allowing the signals of of FF one period ahead of schedule, based on current cycle information of those FFs it operates on.

While assigning a full time cycle for the calculation and propagation of enabling signals, it avoids strict AGFF and data driven timing restrictions. It introduces a locked-form design which defines the power saving per FF. This is based on information-to-clock disabling possibilities, Ability variables, and fan FFs in. The model assumes a leakage curve, which separates the space of the FF into two regs. Not so. Not so. Industry-scale testing revealed a machine power reduction of 22.6 percent, which converted into a torque multiplication of 12.5 cent across the rest of the network.

A rather small information-to-clock button toggles ratio was also recorded, in which detailed power calculations of a wide variety of manufacturing models showed an overall button toggles ratio of 0.02 to 0.05.

A device for flip-flops (FFs) was introduced to address the latter inconsistency, called the information-driven clock gating. If the condition of the FF is not subjected to t In such an effort to reduce the overhead of the gating logic, several FFs are driven by the same clock signal, produced by ORing the activating signals of the actual FFs.

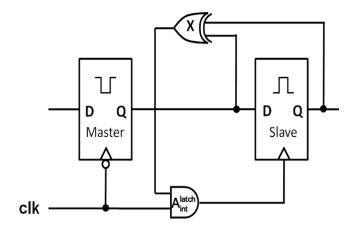

**Auto-Gated Flip-Flops:** The main lock of the FF is opaque on the dropping side of the counter, in which its performance should stable at the earliest until the appearance of the increasing side of the clock, when the main lock is transparent as well as the XOR gate shows if the slaves lock should adjust its condition or not. If it does not, it will interrupt its clock ticking then it will leave. Database-based tiny loops such as clocks, in which each FF's input relies on its administration's output in the registration, were recorded in a reduction in energy. AGFF may also be used in specific reasoning but also with two huge disadvantages.

Fig 2: Auto gated flip-flop

# **Results**

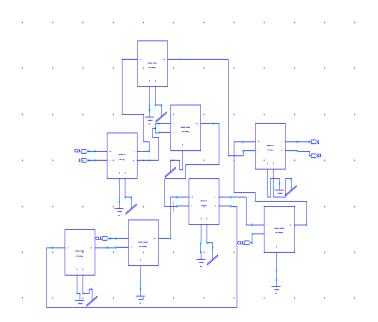

Fig 3: Enhanced AGFF used for LACG

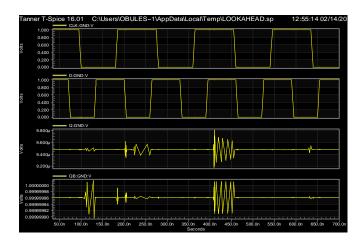

Fig 4: Output waveform of look ahead clock gating

# **Conclusion**

It has been concluded that principle of probabilistic dial-gating (DCG) is focused on the main assumption that perhaps the usage of the circuitry board in a specific cycle is deterministic determined several loops in preparation for some of the stages in a conventional system in the future. DCG dial-gates use this advance knowledge to pipe latches, unused operation units.

# References

- 1. Bipul C. Paul, Amit Agarwal, Kaushik Roy, "Low-power design techniques for scaled technologies", INTEGRATION, the VLSI journal, science direct 39(2006)

- 2. Enoch O. Hwang, "Microprocessor Design Principles and Practices", Brooks / Cole, 2004

- 3. Hai Li, Swarup Bhunia, Yiran Chen, T. N. Vijaykumar, and Kaushik Roy, "Deterministic Clock Gating for Microprocessor Power Reduction",1285 EE Building, ECE Department, Purdue University

- 4. L. Hai, S. Bhunia, Y. Chen, K. Roy, T.N. Vijay Kumar, "DCG: deterministic clock gating for low-power microprocessor design", IEEE Trans. VLSI Syst. 12 (2004), pp.245-254

- 5. Qing Wu, Clock-Gating and Its Application to Low Power Design of Sequential Circuits, IEEE Transactions on circuits and systems-I: Fundamental theory and applications, 47 (103), 2000

- 6. Shmuel Wimer, Design Flow for Flip-Flop Grouping in Data-Driven Clock Gating, IEEE Transactions on very large scale integration (VLSI) systems, 22 (4), 2014

- 7. Shmuel Wimer, The Optimal Fan-Out of Clock Network for Power Minimization by Adaptive Gating, IEEE Transactions on very large scale integration (VLSI) systems, 20 (10), 2012

- 8. Walter Aloisi, Gated-Clock Design of Linear-Feedback Shift Registers, IEEE Transactions on circuits and systems II: Express briefs, 55 (6), 2008

- 9. Weixiang Shen, An Effective Gated Clock Tree Design Based on Activity and Register Aware Placement, IEEE Transactions on very large scale integration (VLSI) systems, 18 (12), 2010

- Yan Luo , Jia Yu , Jun Yang , Laxmi Bhuyan, Low power network processor design using clock gating, Proceedings of the 42nd annual conference on Design automation, June 13-17, 2005, San Diego, California, USA